- 您现在的位置:买卖IC网 > Sheet目录1995 > DSD1792DB (Texas Instruments)IC 24BIT STEREO AUD DAC 28-SSOP

DSD1792

SLES067B MARCH 2003 REVISED NOVEMBER 2006

www.ti.com

51

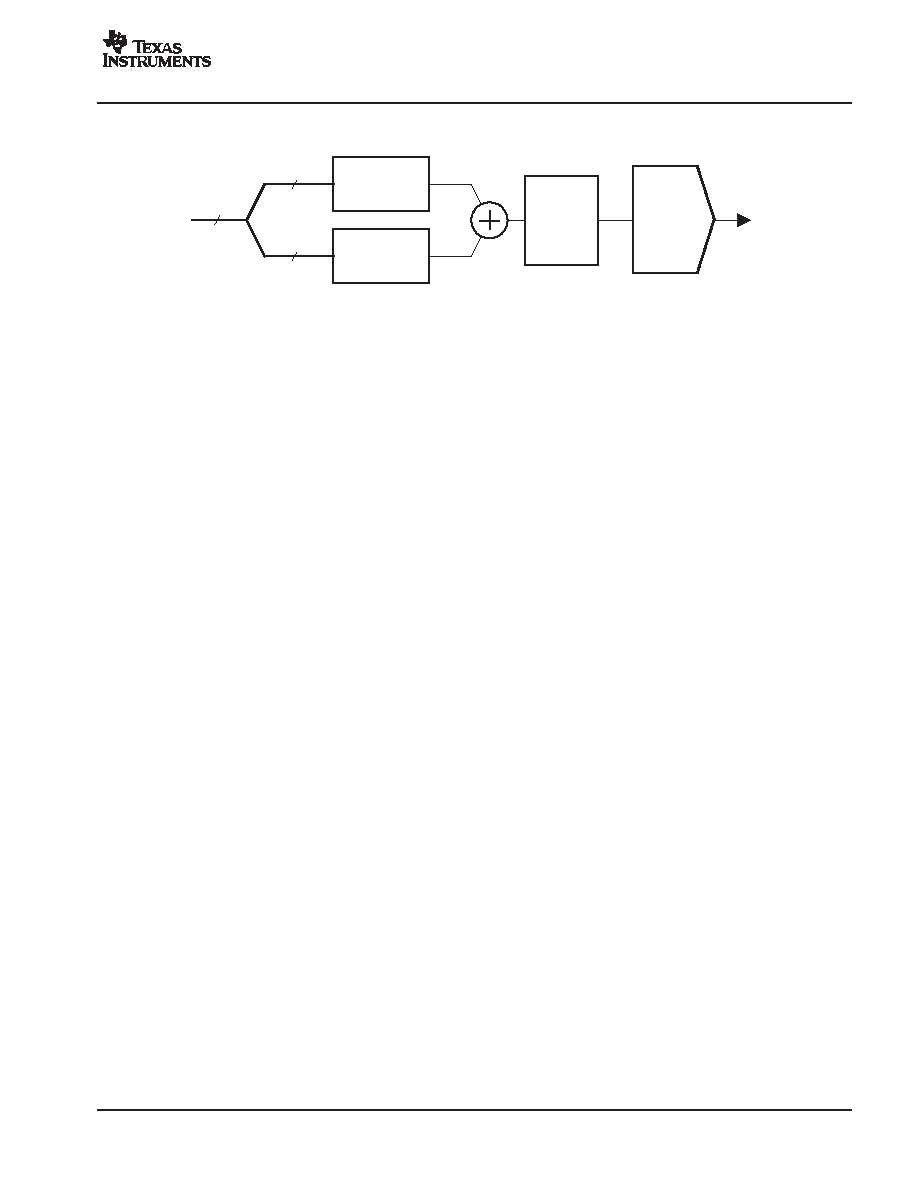

THEORY OF OPERATION

Analog Output

Digital Input

24 Bits

8 fS

MSB

and

Lower 18 Bits

Upper

6 Bits

ICOB

Decoder

3rd-Order

5-Level

Sigma-Delta

Advanced

DWA

Current

Segment

DAC

0–4

Level

0–62

Level

0–66

Figure 62. Advanced Segments DAC

The DSD1792 uses TI’s advanced segment DAC architecture to achieve excellent dynamic performance and

improved tolerance to clock jitter. The DSD1792 provides balanced current outputs.

Digital input data via the digital filter is separated into six upper bits and 18 lower bits. The six upper bits are

converted to inverted complementary offset binary (ICOB) code. The lower 18 bits, associated with the MSB,

are processed by a five-level third-order delta-sigma modulator operated at 64 fS by default. The 1 level of the

modulator is equivalent to the 1 LSB of the ICOB code converter. The data groups processed in the ICOB

converter and third-order delta-sigma modulator are summed together to an up to 66-level digital code, and then

processed by data-weighted averaging (DWA) to reduce the noise produced by element mismatch. The data

of up to 66 levels from the DWA is converted to an analog output in the differential-current segment section.

This architecture has overcome the various drawbacks of conventional multibit processing and also achieves

excellent dynamic performance.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EL5001IRE-T7

IC CLOCK DRIVER 6-CHAN 20-HTSSOP

FT10001L6X

IC RESET TIMER 6-MICROPAK

FT3001MPX

IC RESET TIMER 8-MLP

FT7521L6X

IC RESET TIMER 7.5SEC 6MICROPAK

FT7522L6X

IC RESET TIMER 6-MICROPAK

FT8010UMX

IC RESET TIMER CONF DELAY 10UMLP

FTS125-COO-010.0M

IC GPS BASED TIMING MOD (OCXO)

FTS125-CTV-010.0M

IC GPS BASED TIMING MOD (TCXO)

相关代理商/技术参数

DSD1792DBG4

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1792DBR

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1792DBRG4

功能描述:音频数/模转换器 IC 24B 192kHz Sampl Adv Segment Aud St DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793

制造商:BB 制造商全称:BB 功能描述:24 BIT 192 KHZ SAMPLING ADVANCED SEGMENT AUDIO STEREO DIGITAL TO ANALOG CONVERTER

DSD1793DB

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793DBG4

功能描述:音频数/模转换器 IC 24B 192kHz Sampl Adv Segment Aud St DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793DBR

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793DBRG4

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel